Reed Business Information (RBI\*)

VOICE OF THE ENGINEER

MAR Issue 5/2010 www.edn.com

Signal Integrity Pg 16

Nanotechnology makes strides Pg 19

Design Ideas Pg 37

Supply Chain Pg 57

No good deed goes unpunished Pg 60

### TILT OR NEW GAME? Page 28

PRECISELY MEASURE SETTLING TIME TO 1 PPM Page 20

ENT

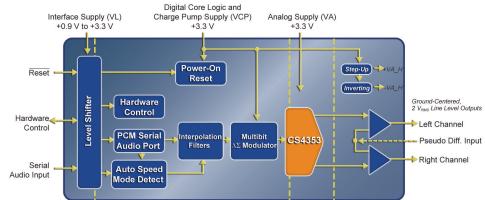

### Finally! A No Compromises Digital-to-Analog Converter CS4353 SIMPLIFIES ANALOG OUTPUT CIRCUITRY, PROVIDING SUPERIOR AUDIO PLAYBACK

Cut the clutter! When it comes to digital-to-analog converters, Cirrus Logic means business. The CS4353 is the only audio DAC to feature an on-chip 2.1 V<sub>RMS</sub> line driver from a single 3.3 V power supply, allowing a 2 V<sub>RMS</sub> voltage after the RC filter. The new architecture not only simplifies the design of analog output section circuitry but it also provides superior quality audio playback with the highest dynamic range and lowest pops and clicks of its kind. This is especially important in applications such as Blu-ray Disc® players, DTV and set-top boxes as they allow for the elimination of multiple system components and lower implementation cost.

#### **CS4353 FEATURES**

- 106 dB Dynamic Range, -93 dB THD+N

- Single-Ended Ground Centered Analog Architecture

- No DC-Blocking Capacitors Required

- Click-Free Stereo Output

- Selectable 1 or 2 Vrms Full-Scale Output

- High PSRR •

- Small 4 mm x 4 mm QFN Package

#### FREE SAMPLE!

Request a free sample of the CS4353 WWW.CIRRUS.COM/4353edna

#### LEARN MORE AT WWW\_CITTIIS\_CON

#### Cirrus Logic. We make it easier for you.

© 2010 Cirrus Logic. Inc. All rights reserved. Cirrus Logic. Cirrus and the Cirrus Logic logo designs are trademarks of Cirrus Logic. Inc. All other brands and product names may be trademarks or service marks of their respective owners EDNA03042011

CIRRUS LOGIC®

#### CS4353 Thermally Enhanced 4 mm x 4 mm QFN Package (shown at actual size)

#### NORTH AMERICA +1 800-625-4084

ASIA PACIFIC +852 2376-0801

JAPAN +81 (3) 5226-7757

**EUROPE/UK** +44 (0) 1628-891-300

# Authorized distributor for more than 440 of the world's most trusted manufacturers.

THE INDUSTRY'S BROADEST PRODUCT SELECTION AVAILABLE FOR IMMEDIATE DELIVERY.

#### 1.800.344.4539 WWW.DIGIKEY.COM

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

Supplier Authorized Distributors

#### Tilt or new game?

29 FPGAs' evolving roles in networking hardware may predict the future of the nearly ubiquitous ICs. by Ron Wilson, Executive Editor

# EDN 3.4.10 contents

#### Precisely measure settling time to 1 ppm

20 Intense, extensive, and protracted effort yields a measurement circuit with 20-bit resolution. *by Jim Williams, Linear Technology*

# **INNOV/TORS**

45 EDN editors have named the five teams profiled in this special section as finalists for Innovator of the Year in our annual Innovation Awards program. Peruse their stories and then cast an online ballot for your favorite team at www.edn.com/innovation20.

- 1 8 billion-transfer/sec PCIe 3.0 test platform integrates new digital-test console

- 12 Aeroflex announces LTE simulator as In-Stat calls LTE the 4G choice

- 14 LED packs 24 chips into tiny package, reduces the need for binning

- 14 Xilinx applies Agilent tools to LTE verification

# DESIGNIDEAS

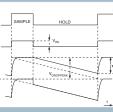

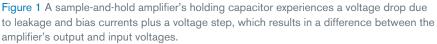

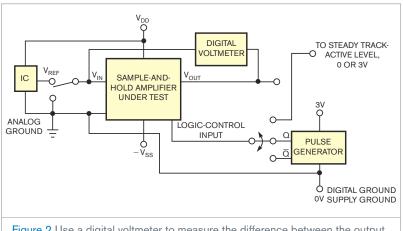

34 Circuit lets you test sample-and-hold amplifiers

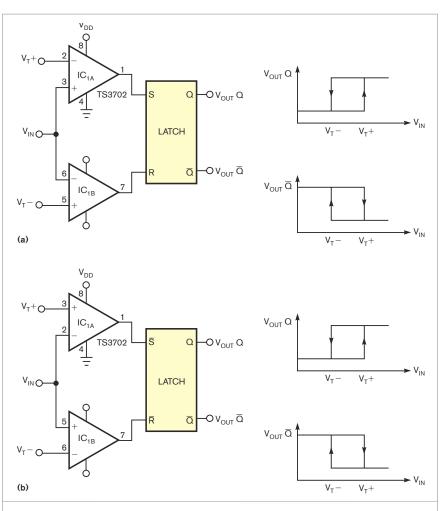

37 Add hysteresis to a voltage comparator

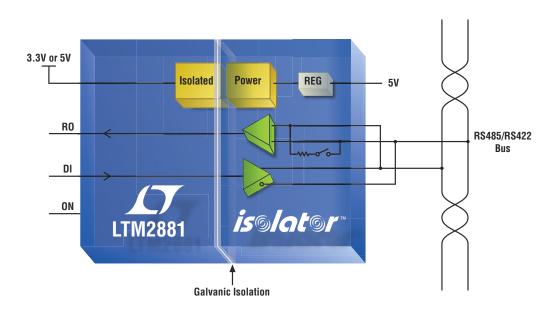

38 Broken-coil detector is simple yet robust

Send your Design Ideas to edndesignideas@reedbusiness.com.

Microsoft Dynamics® CRM integrates information from different sources and puts it in one place, at one time, so everyone in your company sees the information needed to make better decisions faster. It's simple for your sales and support people to use, and it's ready to fit your company right away. So you can spend less time on service calls and more time building stronger relationships.

To learn more about the efficiencies Microsoft Dynamics CRM can create for your business, go to microsoftdynamics.com/manufacturing

Because it's everybody's <u>It</u>business

### Innovative Intelligent Integration

# Sm&rtFusion<sup>™</sup>

FPGA + ARM<sup>®</sup>Cortex<sup>™</sup>-M3 + Programmable Analog

Get Smart, visit: www.actel.com/smartfusion

### **DEPARTMENTS & COLUMNS**

- 6 **EDN.comment:** Toyota, drive by wire, and our failure to learn from experience

- 16 Signal Integrity: Trace scaling

- 19 Inside Nanotechnology: Nanotechnology makes strides in quantum dots, medicine

- 57 **Supply Chain:** Niche distributors specialize for market edge; LEDs help bolster LCD-TV sales; United Kingdom reminds industry of battery regulations

- 58 Product Roundup: Power Sources

- 60 Tales from the Cube: No good deed goes unpunished

#### **EDN**) online contents

#### ONLINE ONLY

Check out this Web-exclusive article:

Acceleration of program execution Look-up tables trade between processing resources and execution time to speed up execution of computational processing. →www.edn.com/article/CA6717542

### Designing with EDs

#### Lighting for the 21st century

Practical, inexpensive HB LEDs (highbrightness light-emitting diodes) are here. Now, what can we do with them, and what will be their impact on electronics and consumers? Read more online. →www.edn.com/leds

# INNO ATION

www.edn.com

Tune in to www.edn.com/ innovation20 to see a list of the innovative engineers and products our editors selected as finalists in the 20th annual *EDN* Innovation Awards and then use the online ballot to cast your vote for the winners in each category. Don't delay! Voting ends March 19. → www.edn.com/ innovation20

EDN @ (ISSN#0012-7515), (GST#123397457) is published semimonthly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US, Jeff DeBalko, President, Business Media; Jane Volland, Vice President, Finance. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2010 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% GST, GST#123397457); Mexico, \$229.99 one year, air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 55, Number 5 (Printed in USA).

# IR's IRF6718 Delivers Industry's Lowest R<sub>DS(ON)</sub>\*

Optimized for Active ORing and Hot Swap Applications

#### Features

- Industry Lowest R<sub>DS(on)</sub> for reduced conduction losses

- Superior electrical and thermal performance in smaller footprint than D<sup>2</sup>Pak

- Dual-sided cooling compatible

- Reduces component count and board space compared to competing solutions

- Compatible with existing Surface Mount Techniques

- RoHS compliant containing no Lead or Bromide

| Part<br>Number | Package<br>Size<br>(mm x mm) | R <sub>DS(ON)</sub> @ 10V<br>typ. (mΩ) | I <sub>D</sub> @TA = 25°C<br>(A) |

|----------------|------------------------------|----------------------------------------|----------------------------------|

| IRF6718        | 7.1 x 9.1                    | 0.5                                    | 270                              |

| Competitor 1   | 10.7 x 15.9                  | 0.7                                    | 180                              |

| Competitor 2   | 5.1 x 6.1                    | 0.95                                   | 60                               |

| Competitor 3   | 5.1 x 6.1                    | 1.5                                    | 65                               |

\* Based on data complied September 2009

#### For more information call 1.800.981.8699 or visit www.irf.com

#### BY RON WILSON, EXECUTIVE EDITOR

# Toyota, drive by wire, and our failure to learn from experience

see from the morning news that Toyota's adventure into the world of embedded software is going badly. The company's second attempt to find a quick fix for unintended acceleration in its conventionally powered vehicles is barely under way, and evidence is already emerging that the underlying problem is likely in the engine controller, not in the pedal's mechanical assembly. Now we hear from Japan that the Prius, Toyota's golden child, has a problem with its brake-bywire control system.

Decades ago, Audi accidentally intro duced drive by wire with its advanced cruise control on the Audi 5000. The cars were allegedly subject to spontaneous acceleration, a problem the company blamed on operator error. At the time, researchers at another European high-end auto company claimed to have uncovered a problem in Audi's engine-control firmware and reproduced the acceleration without requiring a driver to mistake the gas pedal for the brake. The ensuing liability litigation, however, extinguished all hope of diagnosing and documenting the problem so that the rest of the real-timesoftware community could avoid it.

All this came to mind when I attended a panel on achieving quality closure at last month's DesignCon in Santa Clara, CA. Despite the subject of the panel—achieving quality closure—the issue of software sat like an elephant in the corner of the room, awaiting notice. One of the panelists pointed out that the most serious quality problem in IC designs now is not the quality closure on the hardware but the integrity of the firmware and software that will run on the chip. There simply is no systematic

Along came C, Unix, and the cult of the hobby programmer, and the entire notion of formal correctness vanished under a smokescreen of hacking.

approach to ensuring the quality of an integrated hardware/software system.

This situation is a tragedy. Work was well under way 30 years ago on the problem of formally proving software correctness. One company had designed a completely deterministic microprocessor that made it possible to mathematically prove all of the possible trajectories of a code set. Computer scientists such as Edsger Dijkstra were making strides in a method for creating formally proven software. But along came C, Unix, and the cult of the hobby programmer, and the entire notion of formal correctness vanished under a smokescreen of hacking.

Now, after decades invested in metrics-driven verification, formal verification, and methodology management, designers find that their chips don't work as expected because the software is still being "verified" by feeding it test cases until the schedule expires. Consumers find that their cars run into these problems for the same reason, and the press blames the problem on "electronics."

Once again, as in Audi's day, it is safe to conclude that a gag order as part of a class-action settlement will screen whatever accurate diagnostic work takes place on the Toyota problems so that no one in the industry can benefit from what Toyota engineers learn. In that way, we can repeat the situation with the next generation of software-governed systems, a new set of executives can avoid blame for the tragedies, and a new set of lawyers can make their fortunes from the resulting litigation.

The only parties in this little tragedy with an interest in improving the state of the art are the engineers, whom no one will consult, and the victims, whom the lawyers will silence. It would be better for everyone if it were a principle of civil law that, when a failure inflicts damage, the vendor and independent parties must place all of the diagnostic information they find into the public domain, and the courts may not use this information to assess or assign damages. Such a notion might somewhat restrict the income opportunities of litigators, but it would unquestionably assist the engineering community in learning from its mistakes.EDN

Contact me at ronald.wilson@reed business.com.

The First Truly Global Foundry

Congratulations to the new GLOBALFOUNDRIES, the merged operations of GLOBALFOUNDRIES and Chartered.

To our continued mutual success from your Global Customers and Partners

Advanced Technology – It's in our Genes

# CST STUDIO SUITE 2010 for SIXPI and EMC/EMI analysis

### Next generation 3D electromagnetic simulation

The best available tool for 3D EM simulation has evolved into version 2010. With a user friendly interface, easy data exchange to and from other software tools, a choice of first class solvers and world class post-processing tools, you can leverage the latest developments in 3D electromagnetics to bring designs to market faster and with lower risk.

Choose CST STUDIO SUITE 2010 – complete technology for 3D EM.

CHANGING THE STANDARDS

#### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417;

rpratt@reedbusiness.com ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617;

judy.hayes@reedbusiness.com EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-734-8418;

rnelson@reedbusiness.com **EXECUTIVE EDITOR** Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesianideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Web Operations Specialist

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

####

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE Graham Prophet, Editor, Reed Publishing +44 118 935 1650; aprophet@reedbusiness.com

EDN ASIA Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn

Jeff Lu, Executive Editor jefflu@rbichina.com.cn EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.geffreemag. com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, C0 80129-2345. Include your mailing label.

# **MAXIMUM RELIABILITY**

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance

- through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

#### Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

# EXTREME EVOLUTION

Introducing the RX Family from Renesas. The next-generation microcontrollers for communicating anytime, anywhere, and with anyone and anything.

- Extremely high performance: 1.65DMIPS/MHz, up to 200MHz

- Extremely small code: up to 30% smaller than previous Renesas MCUs

- Extremely low power consumption: 30µA/MHz (typical) for the core

- Extremely high integration: with up to 4MB of extremely fast embedded Flash

Stay tuned. The evolution continues.

Check the website for details.

## www.america.renesas.com/ReachRX/a

RenesasTechnologyCorp.

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

# 8 billion-transfer/sec PCle 3.0 test platform integrates new digital-test console

gilent Technologies has introduced a test platform that includes a digital-test console, which provides a complete integrated protocol analyzer and exerciser for one- to 16-lane implementations of the PCle (Peripheral Component Interconnect Express) 3.0 specification. PCle 3.0 is currently under development within the PCI-SIG (PCI Special Interest Group). The console offers the industry's largest capture buffer and fastest download interface.

The company designed the console to assist with and provide accurate test results during the development of PCIe 3.0 and products that support and incorporate it. The transition to PCIe 3.0 requires test engineers and validation labs to address the new specification's higher bus speeds and backward-compatibility requirements and to adapt to changes in the bus's encoding scheme and several new advanced protocol features. The console provides an ESP (equalization-snoop-probe) interface, which reliably captures data at 8 billion transfers/sec; it also incorporates an LTSSM (link-training-sequence-state-machine) exerciser for validating new encoding- and protocol-state-machine designs and a flexible GUI (graphical user interface) to aid in debugging the advanced protocol.

The test platform includes a large collection of tools for testing and validating PCIe 3.0 requirements from the electrical layer to the protocol layer. These tools include the 90000-Series Infiniium oscilloscopes, which integrate de-embedding capabilities as well as CTLE (continuous-time-linear-equalization) software that ensures the electrical compliance of future PCIe 3.0 devices; the 86100C Infiniium DCA-J (digital-communication analyzer/jitter), which provides one-button ease of use and performs precision waveform analysis as well as jitter, TDR (time-domain-reflectometer), and S (scattering)-parameter measurements; and the N4903B J-BERT (jitter/bit-error-ratio tester), a high-performance serial BERT that performs complete jitter-tolerance testing for accurate receiver characterization.

The platform also includes the N5990A testautomation software for complete automation of PCIe-compliance testing using the J-BERT, ParBERT (parallel BERT), and other Agilent instruments and the ADS (Advanced Design System), a software suite that includes a complete set of simulation tools ranging from frequency-, time-, numeric-, and physical-domain simulation to electromagnetic-field simulation for design characterization and optimization. The average system price is \$100,000.

-by Dan Strassberg

Agilent Technologies, www.agilent.com/

find/pci-express, www.agilent.com/find/

pciexpress\_backgrounder.

FEEDBACK LOOP "SIP (system-inpackage) technologies can provide the best of both worlds but with one important caveat: In the end, reliability is a function of the weakest link. So, for highvolume applications, SOC (system on chip) is a good way to go." -Reader Dave Anderson, in

*EDN*'s Feedback Loop, at www. edn.com/article/CA6715766. Add your comments.

This digital-test console is the nerve center of a platform for design and verification testing of one- to 16-lane implementations of the 8 billion-transfer/sec PCIe 3.0 bus.

# pulse

# Aeroflex announces LTE simulator as In-Stat calls LTE the 4G choice

o speed up real-world testing of mobile handsets for LTE (long-termevolution) networks before network deployment, Aeroflex has introduced a one-box test system for cell-phone signalfading simulation.

In-Stat analysts note that, although WiMax (worldwide operability for microwave access) appeared to be a competitor for 4G, the battle is now largely over, and the success of 3G, HSPA (high-speed-packetaccess), and HSPA+ networks will impede LTE's deployment as mobile operators leverage their installed infrastructure (see "Getting to 4G through design and test," *EDN*, April 9, 2009, pg 38, www.edn.com/ article/CA6648778). "LTE still has several glaring issues," cautions Allen Nogee, an In-Stat analyst. These issues include lack of spectrum, SNR (signalto-noise ratio), and the lack of an established patent and royalty pool. "The shift toward 4G LTE will be gradual and protracted," he says.

Nevertheless, LTE deployments will begin this year, with North America and Asia/ Pacific being the first regions to roll out. As deployment progresses, the demand is growing to meet all LTE requirements, including fading profiles that 3GPP (Third Generation Partnership Project) specifies in 36-521-1. Aeroflex's 7100 Series test platform provides The simulator supports all 3GPP fading profiles, allowing users to determine whether their devices conform to 3GPP test specifications.

fading simulation that meets or exceeds all 3GPP requirements, as well as flexibility in allocating cells and fading taps for LTE user equipment without the need for manual reconfiguration. The series features fully repeatable test scenarios with

Aeroflex's 7100 Series test platform provides fading simulation that meets or exceeds all 3GPP requirements, as well as flexibility in allocating cells and fading taps for LTE user equipment.

#### **DILBERT By Scott Adams**

the fading simulator. These scenarios include the emulation of dynamic environments and realistic and accurate testing of MIMO (multiple-input/ multiple-output) situations.

Fading simulators combine with noise generators to modify RF signals that the LTE-system simulator transmits and emulate degradations that real-life obstacles, such as buildings and foliage, introduce into the radio channel. For LTE developers who must profile signal fading on mobile handsets to meet 3GPP requirements before a network is available, the 7100 Series fading simulator allows engineers to perform realistic signal-fading simulations in a reliable and repeatable lab environment.

With the LTE future in mind, the 7100 Series fading simulator supports all LTE bandwidths to 20 MHz with a frequency range as high as 6 GHz. The simulator supports all 3GPP fading profiles, allowing users to determine whether their devices conform to 3GPP test specifications.

Employing Aeroflex's RF and baseband technology, the 7100 Series digital-radio test set supports both RF parametric and protocol testing for LTE-terminal devices. Targeting the R&D market—from components to handsets—the series simulates a network from the physical layer to the core-network IP infrastructure.

A typical system with two RF carriers and  $2 \times 2$  MIMO sells for approximately \$100,000. Customers can license and install the \$10,000 fading-simulator software option and on units in the field. For more on these developments, go to www.edn.com/pa.

-by Rick Nelson

Aeroflex, www.aeroflex.

com.

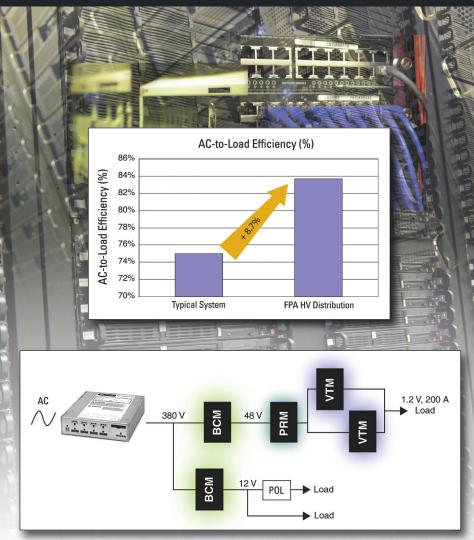

# All of the Savings None of the Loss

#### HV Bus Converters Enable AC-to-Load Efficiency Increase of 8.7%

| BCM<br>Model No. | Input<br>Voltage<br>(V) |           |     | Output<br>Voltage<br>(V) | Output<br>Power<br>(W) | Output<br>Current<br>(A) |

|------------------|-------------------------|-----------|-----|--------------------------|------------------------|--------------------------|

|                  | Nom                     | Range     | Nom | Range                    |                        |                          |

| VIB0002TFJ       | 380                     | 360 - 400 | 48  | 45.00 - 50.00            | 325                    | 7.0                      |

| B384F120T30      | 380                     | 360 - 400 | 12  | 11.25 – 12.50            | 300                    | 25.0                     |

| VIB0003TFJ       | 350                     | 330 – 365 | 44  | 41.25 – 45.60            | 325                    | 7.7                      |

| VIB0001TFJ       | 350                     | 330 - 365 | 11  | 10.30 - 11.40            | 300                    | 28.0                     |

- High power density: Up to 1120 W/in<sup>3</sup>

- 380 V to 1.2 V, 200 A conversion in 4.5 in<sup>2</sup>

- Low noise ZVS ZCS MHz switching

- >95% efficiency

For high power computing and telecom systems, HV BCM<sup>™</sup> bus converters are high efficiency, low noise, high power density system building blocks that enable the highest possible distribution efficiency.

As part of a Factorized Power Architecture solution, the HV BCMs efficiently power sub 1.0 V processor and memory arrays while providing 12 V for disk drives and legacy loads.

#### To order call 1-800-735-6200 or email custserv@vicorpower.com

#### Products in mass production and available from stock

#### vicorpower.com/hvbcm/edn

# pulse

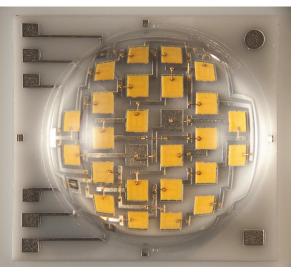

# LED packs 24 chips into tiny package, reduces the need for binning

ith Cree's announcement of its XLamp MPL EasyWhite LED, the company moves another step forward in its quest to eliminate "binning" from the vocabulary of LEDlighting-application designers. The XLamp MPL EasyWhite can provide as much as 1500 lumens at 250 mA. This bestcase number represents a pulsed rather than a constantly on drive current. With proper drive electronics and heat sinking, however, the LED can deliver equivalent light output to-and consume 78% less power than-that of a traditional 3000K, 75W BR-30 halogen light bulb. This performance meets the Energy Stardefined efficacy-per-lumen requirements for integral LED lamps (www1.eere.energy.gov/ buildings/ssl/energy\_star\_ criteria.html).

The EasyWhite series frees light-application designers from the need to match the color output of multiple LEDs in each light-bulb fixture. Customers like to see a uniform color from lights: Imagine a string of track lights using the familiar PAR-38 bulbs—some a warm white and others a cool white. This arrangement would be distracting and unattractive. To address that problem,

In our Feb 4, 2010, cover story, a sentence on pg 31, repeated in the "At a glance" sidebar on pg 28, reads, "Designers can now implement baseband functions in FPGAs and ASICs that they once had to implement in software." It should have read "Designers can now implement baseband functions in software that they once had to implement in FPGAs and ASICs." For the full article, see "Wireless to go," *EDN*, Feb 4, 2010, pg 26, www.edn.com/article/CA6716491.

The top-side contacts for the XLamp MPL free the LED from a PCB for mounting. You can mount the MPL directly onto an aluminum heat sink.

LED manufacturers traditionally sorted the chips in color bins. Light manufacturers would mix and match from these bins to get a uniform color, but this approach requires a large inventory of LEDs to meet the productionline needs for a variety of bins. The idea of binning is also confusing. Traditional light sources require only two specifications: color temperature and light output. Cree is attempting to simplify the specification and reduce inventory by eliminating or at least reducing the need for binning.

The MPL also eliminates pixelation, the appearance of several tiny dots of light as the source, by densely packaging 24 LED chips into a 12×13mm package that Cree believes is 72% smaller than the nextsmallest alternative. In contrast, many manufacturers of traditional multichip LEDs commonly pack only four chips into a package. The XLamp MPL sells for less than \$20 each (high volumes).

How does the MPL series, the first member of the Easy-White family, fit in with the MC-E series of LEDs, which the company announced in late 2009? The MC-E has only four chips in its package. The devices can produce as many as 560 lumens at 700 mA and act as replacements for 20 to 35W halogen light bulbs in indoor-lighting applications, such as accent, track, and pendant lighting.

−by Margery Conner **Cree**, www.cree.com.

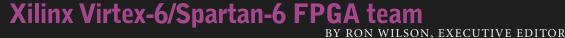

#### XILINX APPLIES AGILENT TOOLS TO LTE VERIFICATION

Agilent Technologies has announced that Xilinx has employed Agilent EEsof SystemVue software plus Agilent test equipment, including the Agilent N5106A PXB baseband generator and channel emulator, to verify 3GPP (Third **Generation Partnership** Project) LTE (long-termevolution) hardware blocks using test vectors from a credible algorithmic reference. The Xilinx wireless engineering team needed to develop production-quality LTE uplink LogiCore IP (intellectual property) for Xilinx eNodeB customers. Xilinx had to verify all LTE algorithms and hardware-IP cores against published standards, but its engineers found that available test-vector-creation methods either lacked the fine parameterization and flexibility necessary for testing LTE PHY (physical-layer) algorithms and blocks or lagged behind updates to the standard.

Xilinx used Agilent SystemVue and the W1910 LTE baseband verification library to create highly specific LTE test vectors, which Xilinx downloaded to the Agilent N5106A PXB baseband generator and channel emulator, adding fading and control to the real-time test environment. For more, go to www.edn. com/pb.-by Rick Nelson Agilent Technologies, www.agilent.com.

Xilinx, www.xilinx.com.

03.04.10

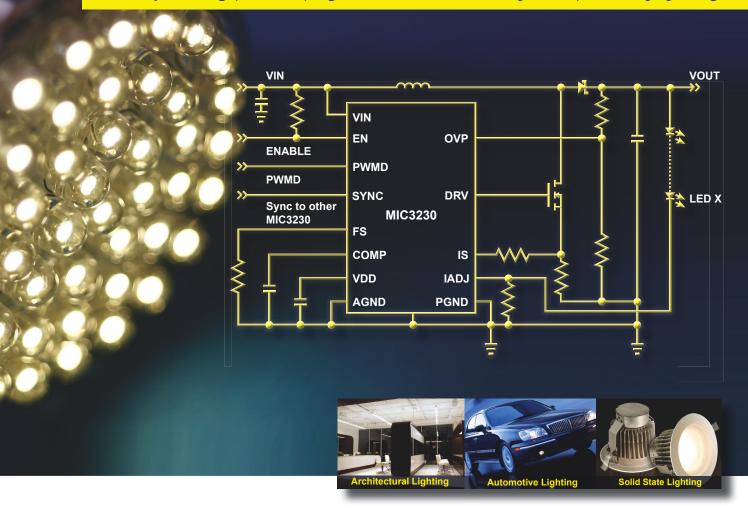

# Bringing the Power to Light<sup>™</sup> with High Performance LED Drivers

Wide Input Voltage, Low EMI, High Power LED Drivers. Easy to Use, Flexibility by Design.

**The** rapid growth of LED lighting applications in commercial, industrial and automotive markets has led to a wide variety of technical requirements for LED drivers. Micrel is meeting these challenges with its family of high performance LED drivers.

For example, the new 45V input, 70W, 3% accuracy constant current boost controllers like MIC3230/1/2 delivers the performance and flexibility needed. In addition to the PWM dimming and synchronization capability, these LED drivers also offer dither feature for EMI reduction up to 10dB thus providing an unparalleled performance for your solid state lighting applications.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel.com/mic3230.

Ideal for use in:

- Solid State Lighting

- Street Lighting

- General Illumination

- Architectural Lighting

- Constant Current Power Supplies

|                    | MIC3230                      | MIC3231                      | MIC3232      |

|--------------------|------------------------------|------------------------------|--------------|

| Input Voltage      | 6V to 45V                    | 6V to 45V                    | 6V to 45V    |

| Synchronization    | Yes                          | No                           | No           |

| Dither             | No                           | Yes                          | No           |

| Frequency<br>Range | Adjustable<br>100kHz to 1MHz | Adjustable<br>100kHz to 1MHz | Fixed 400kHz |

| Package            | 16-Pin TSSOP<br>12-Pin MLF®  | 16-Pin TSSOP<br>12-Pin MLF®  | 10-Pin MSOP  |

© 2010 Micrel, Inc. All rights reserved. Micrel is a registered trademark of Micrel, Inc. Bringing the Power to Light is a trademark of Micrel, Inc. MLF is a registered trademark of Amkor Technology, Inc.

SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

### Trace scaling

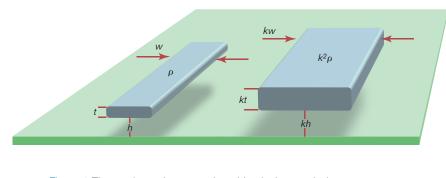

magine a microstrip trace (left side of **Figure 1**). Now scale up that trace, producing a new trace exactly k times larger in width, thickness, and height. It may surprise you to discover that this process of cross-sectional scaling does not change the per-unit-length values of trace capacitance, C, or trace inductance, L. The formulas for those quantities involve only ratios among width, thickness, and height. The absolute values don't matter. A six-mile-wide trace sitting atop a proportionately huge slab of FR (fire-retardant)-4 material enjoys the same exact capacitance per inch as its smaller cousin.

I mention this rule in case you encounter a PCB (printed-circuit-board) trace with dimensions smaller than the minimum values that your signalintegrity simulation tool allows. That scenario can easily happen in multichip-module work involving aluminum traces on silicon substrates. If that situation happens, use the rule of cross-sectional scaling to fake out your simulation tool using physical dimensions large enough to work with the tool but electrically identical to your original circuit.

The rule of cross-sectional scaling

preserves the per-unit-length values of capacitance and inductance, but what about other parameters necessary for lossy-line calculations? You can handle them, too. The G parameter, conductance, describes the dielectric properties of the material surrounding your conductors. Specify the same dielectric material in your expanded circuit as the original, and you get the identical dc leakage and dielectric-loss performance. That part is easy. The *R* parameter represents the trace's resistance, and you must adjust it. **Figure 1** illustrates the cor-

Figure 1 These microstrip traces share identical transmission parameters.

rect procedure. The trace on the left comprises a conductor with a resistivity of  $\rho$  ohm-meters. The trace on the right scales that resistivity by a factor of  $k^2$ .

You can check the resistance-scaling procedure by thinking about the formula for the resistance of a long, thin copper bar. That formula equals the resistivity of copper, times the length of the bar, divided by the cross-sectional area of the bar. If you change the bar height and width by k, its cross-sectional area changes by  $k^2$ , decreasing the resistance by  $k^2$ . If you then multiply the resistivity of copper by  $k^2$ , the total resistance returns to its original value.

The resistivity-scaling procedure also properly handles skin-effect resistance. To understand this concept, you must remember that skin depth equals  $\sqrt{2\rho/(2\pi f)\mu}$ , where f is the frequency of operation, and  $\mu$  is the magnetic permeability of the dielectric material. You must also know that what matters in a lossy-line problem is not the absolute value of skin depth but its value as a proportion of trace thickness. The skin-depth formula shows that scaling  $\rho$  by  $k^2$  scales the skin depth by *k*, which renders the ratio of skin depth to trace thickness (also scaled by k) the same as in the original trace.

I do not know whether your simulator will allow you to make the required changes in resistivity. If it does, you can build a new layer stack with the same actual per-unit-length values of resistance, inductance, conductance, and capacitance as your original configuration, only at a physical scale acceptable to your simulator. Your simulator won't know the difference.**EDN**

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

### Look to New Digital Optocouplers for Low Power and High Noise Rejection

#### Introduction

For many years optocouplers have reduced system noise, provided high voltage insulation, and made systems reliable and safe. Although these basic system requirements remain, Avago has developed new isolation technology and architectures that reduce power consumption substantially and increase design flexibility without compromising high voltage protection and noise rejection.

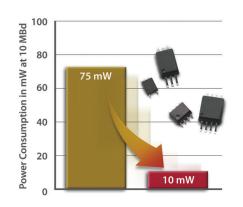

Figure 1. ACPL-x6xL power vs. first generation optocouplers.

Avago's new ACPL-x6xL ultra-low power, 10 MBd CMOS digital optocouplers have the performance needed in modern communication interfaces that use SPI and I<sup>2</sup>C serial interfaces, long distance RS-485 multipoint communications networks, CAN bus interfaces, microprocessor and microcontroller interfaces, and A/D and D/A converters. Table 1 shows the overall ACPL-x6xL family characteristics. Performance over temperature, –40 to 105°C, low LED drive current, continuous working voltages of up to 1,140 Vpeak and transient overvoltage protection of up to 8,000 Vpeak are ideal for industrial, medical, test and measurement and computer peripheral applications.

#### **Key ACPL-x6xL Series Features**

- Low current LED input allows direct drive from microprocessor CMOS outputs

- 35 kV/µs dynamic and static common mode rejection no compromise on noise immunity!

- Controlled output slew rate over a wide range of load conditions

- Easy configuration for inverting and non-inverting operation

- Optical isolation technology is certified for safe insulation at continuous working voltages from 560 Vpeak to 1140 Vpeak and with transient voltages of 6 kVpeak / 8 kVpeak

#### Table 1. Key ACPL-x6xL family features.

| Parameter                   | Specification          |

|-----------------------------|------------------------|

| Propagation Delay           | 80 ns (max)            |

| Skew between any two parts  | 30 ns (max)            |

| Pulse width distortion      | 30 ns (max)            |

| LED forward current         | 1.6 mA                 |

| Icc supply current          | 1.3 mA (max)           |

| Common Mode Noise Rejection | 35 kV/µs at 1000 V     |

| Supply voltage              | 2.7 to 5.5V            |

| Temperature range           | -40 to 105°C           |

| Continuous working voltage  | 560 Vpeak / 1140 Vpeak |

| Transient overvoltage       | 6 kVpeak / 8 kVpeak    |

#### Architecture

The low LED current needed to switch the new optocouplers series makes it possible to drive the input LEDs directly from most microprocessor outputs. To simplify your circuit design, all timing parameters are specified with fixed input resistor configurations, rather than current, for 3.3 V and 5 V signal levels across the temperature range. The push-pull CMOS outputs eliminate external pull-up resistors.

#### LED Inputs are Ideal in Noisy Environments

Common mode noise can be a significant problem in data communication applications, especially in industrial environments where electrical motors, sensors and programmable logic controllers are connected together. In such systems, isolators reduce noise levels and enhance signal performance. All isolators, regardless of technology, have a parasitic capacitive coupling between the two isolated sides of the component. A noise transient occurring on the output side may cause an unwanted voltage rise on the input side. This could result in false-triggering of the input or even latch-up of high impedance logic inputs. Optical isolators with LED inputs are ideal in environments with high levels of common mode noise.

The attenuation of the light signal through the internal, optically transparent insulation material is low, so the distance through isolator can be kept high in the new ACPL-x6xL family. A direct consequence of the large separation distance is a low parasitic capacitance. In other words, the unwanted coupling between the two sides is kept to a minimum.

The "split resistor" input LED drive approach balances the impedance across the LED input. A common mode noise voltage rise on the LED is symmetrical and therefore cannot switch the LED on. In addition, the ACPL-x6xL family LED inputs have a relatively high 70 pF input capacitance. The series connected LED and current

#### The Avago Advantage Technical Notes

limiting resistor form a low pass filter that reduces noise transients further. An internal Faraday shield also minimizes the effects of common-mode noise.

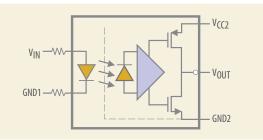

Figure 2. Split input resistors give balanced impedance for higher CMR and lower noise.

#### New Specification: Dynamic Common Mode Rejection

For the new ACPL-x6xL product family, Avago has an additional definition for common mode noise rejection that reflects how the device operates in an application. First generation test setups for common mode noise rejection are based on static performance with the input tied directly to Vcc or ground. Our new Dynamic Common Mode Rejection specification is based on common mode performance during data transmission. The static and Dynamic Common Mode Noise Rejection of the ACPL-x6xL family is 35 kV/µs.

#### Design Flexibility: Inverting and Non-inverting Operation

The output stage is inverting but it is easy to configure ACPL-x6xL devices for either inverting or non-inverting operation. In Figure 2, change Vin to Vcc and GND1 to Vin to obtain a non-inverting configuration.

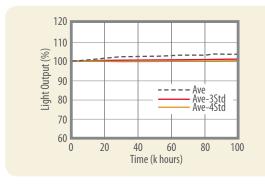

#### Long Life: LED Light Output over Time and Temperature

An optocoupler's life time is a strong function of input LED quality. Avago produces high reliability LEDs for optocouplers at its in-house facility. The infrared, AlGaAs LED used in the ACPL-x6xL family provides excellent stability over both temperature and time. As shown in Figure 3, light output power (LOP) is essentially unchanged after 100,000 hours of operation. Graphs showing performance over temperature are in the product data sheet.

#### Figure 3. LED light output power, LOP, stability over time

For isolators, fundamental trade-offs exist between power consumption, noise rejection and switching speed. The new ACPL-x6xL optocouplers series has been developed to achieve best-in-class noise rejection and power consumption without compromising safety specifications.

### Design Example: Isolated SPI Interface Benefits from Slew-rate Controlled Outputs

In many applications, such as SPI and I<sup>2</sup>C serial interfaces, stable switching parameters over time and temperature are far more important than the actual device switching speed.

The maximum data rate for a serial interface is limited by the skew / synchronization between signals on the data and clock lines rather than the optocoupler's absolute propagation delay. Increasing the absolute switching speed of an isolator decreases noise rejection. Rather than reducing propagation delay, Avago focused on new design features that reduced skew and enhanced signal quality. One such feature is slew-rate controlled outputs.

Differences in line capacitance can lead to differences in rise and fall time between two channels. In the case of an SPI interface, the clock and signal lines may have different fan-out capability. The output on the ACPL-x6xL family is able to precisely control the output rise and fall times over a wide range of load capacitances. The propagation delay difference (skew) between any two channels in the ACPL-x6xL family is specified at 30 ns maximum over temperature.

#### Supply Voltage Range and Glitch-Free Outputs

Besides being power efficient, the new ACPL-x6xL is able to deliver stable switching performance across a 2.7 V to 5.5 V supply voltage range plus the outputs are glitchfree during power up and power down. A circuit similar to under-voltage lockout ensures an output is at a known state during power up or power loss.

#### Summary

Avago's new generation of 10 MBd digital optocouplers provide the power efficiency modern designs need without sacrificing high voltage insulation or noise isolation performance. Outputs are slew-rate controlled for fast operation and stability over varying loads. All devices feature glitch-free outputs during power up and power down.

As Table 2 shows various package options are available. All devices are RoHS-6 compliant and meet all international safety requirements.

#### Table 2. Ultra low power 10 MBd digital optocouplers

| Part No.  | Package | Chnl | lsolation Voltage<br>(Vrms/min) | Working Voltage<br>(Vpeak) |

|-----------|---------|------|---------------------------------|----------------------------|

| ACPL-061L | SO-8    | 1    | 3750                            | 560                        |

| ACPL-064L | SO-8    | 2    | 3750                            | 560                        |

| ACPL-M61L | SO-5    | 1    | 3750                            | 560                        |

| ACPL-W61L | SSO-6   | 1    | 5000                            | 1140                       |

| ACPL-K63L | SSO-8   | 2    | 5000                            | 1140                       |

An evaluation aboard is available to all qualified designers by contacting your local Avago distributor or representative.

Contact us for your design needs at: **www.avagoresponsecenter.com/401**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2010 Avago Technologies

### INSIDE NANOTECHNOLOGY

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

# Nanotechnology makes strides in quantum dots, medicine

anotechnology is an emerging area with contributions from both established companies and start-ups. One participant in the industry, eight-year-old Nanosys Inc (www.nanosysinc.com), is working on commercializing materials made with nanoparticles and nanotechnology devices. The company recently announced its Quantum-

Rail lighting system for LG mobile-phone applications. This announcement represents the first major consumer-product application of the

company's quantum-dot-phosphor nanoscale-coating technology. You can apply the coating to LEDs to help clarify the color spectrum and reduce power consumption in backlit-LED applications. The technology enables mobile devices to display a truer color even in daylight. You can also use the technology in large LED arrays, such as those in LCD televisions. In those applications, the coating technology reduces power consumption, improves color and clarity, and screens the lowend "tail" light from the LEDs that causes some TV sets to interfere with IR (infrared) remote units on set-topbox or other audio/video equipment.

The Nanosys announcement heralds the arrival of nanotechnology products from other companies that will soon be entering the market and shows that the typical eight- to 10-year gestation period for breakthrough technologies to reach commercialization is now reaching an end. For example, nanomedicine is now emerging as a major topic of investigation. To help solidify the topics in this area and to determine the best direction for commercialization, the ASME (American Society of Mechanical Engineers) held the First Global

#### The typical eightto 10-year gestation period for breakthrough technologies to reach commercialization is now reaching an end.

Congress on NEMB (nanoengineering for medicine and biology, www.asme conferences.org/NEMB2010), a threeday event that took place last month in Houston.

Nanomedicine is an interesting field because a lot of the research and product development is coming from the traditional DSM (deep-submicron)-IC industry. Giving one of the plenary talks at the event was Mauro Ferrari, PhD, director of nanomedicine and deputy chairman of the department of biomedical engineering at the University of Texas Health Science Center. The NEMB event also showcased materials, characterization, modeling, circuit, and NEMS (nanoelectromechanical-system)-design presentations.

In materials development, nanotechnology parallels the strides researchers are making in subwavelength-electronics-semiconductor and semiconductor-process development. Presenters at the event discussed spincoating techniques, carbon and magnetic nanotubes, and shadow-edge lithography for the creation of nanochannels. These nanochannel structures are finding use in molecular microfluidic applications and in waveguides for monolithic optical circuits. Researchers on the circuit side of nanomedicine are examining ultrahigh-sensitivity traditional circuits in which the sense levels are molecular rather than macroscopic. Developers presented polysilicon-nanowire FET chemical sensors; piezoresistive cantilevers for explosive vapor, which has applications in security and health care; nonlinear-resonance NEMS and MEMS (microelectromechanical-system) biosensors; and wireless pointof-care patient-monitoring systems.

To supplement the circuit design, presenters discussed a new development in modeling and the need for a basic understanding of the nanoscale phenomenon. For example, they covered electron-transportation behavior in single-crystal silicon nanowires, the design of nanotip sensors, and modeling and simulation of the motion of bio-inspired swimming microrobots. Semiconductor-processing techniques and physics-based modeling for the optical and medical sectors are strong extensions of the traditional electronic-semiconductor business. The large growth and R&D in these sectors will be around for several decades. Silicon and carbon are still holding strong as the engineering materials of choice.EDN

Pallab Chatterjee is vice chairman of the IEEE San Francisco Bay Area Nanotechnology Council. You can reach him at pallabc@siliconmap.net. INTENSE, EXTENSIVE, AND PROTRACTED EFFORT YIELDS A MEASUREMENT CIRCUIT WITH 20-BIT RESOLUTION.

# PRECISELY

# measure settling time to 1 ppm

BY JIM WILLIAMS • LINEAR TECHNOLOGY

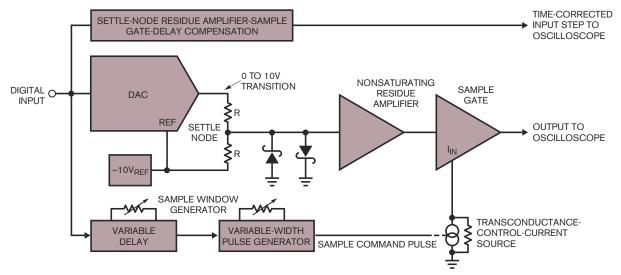

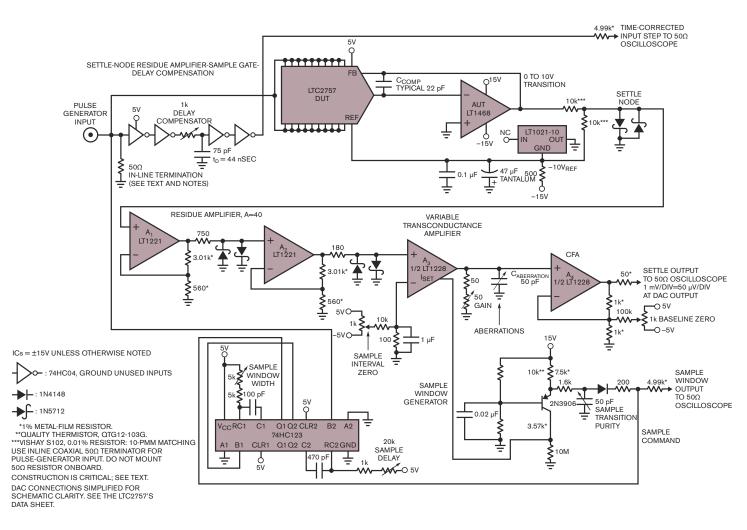

nstrumentation, function generators, inertial navigation systems, ATE (automatic test equipment), medical apparatus, and other precision applications now require 18-bit converters. The resolutions of these converters are so precise that measuring various performance parameters is difficult. DACs' dc specifications are relatively easy to verify, but their ac specifications require more sophisticated approaches to produce reliable information. A DAC's settling time is the elapsed time from an input code application until the output remains within a specified error band around the final value. The settling time of a DAC and its output amplifier is difficult to determine at 18-bit, or 4-ppm, resolution. To measure an 18-bit DAC,

you must use measurement techniques with 20-bit, or 1-ppm, resolution for settling times as short as 265 nsec. Manufacturers usually specify DACs' settling times for a full-scale 10V transition.

Measuring anything at any speed to 20-bit, or 1-ppm, resolution is difficult (see **sidebar** "Components for 18-bit digital-to-analog conversion"). Dynamic measurement to 20-bit resolution is particularly challenging. Reliable 1-ppm DAC-settling-time measurement constitutes a difficult problem requiring exceptional care in approach and experimental technique. You can use an oscilloscope to accurately display DAC-settling-time information for a 10V step with 1-ppm, or  $10-\mu$ V, resolution within 265 nsec. The approach permits observation of small amplitude information at the excursion limits of large waveforms without overdriving the oscilloscope.

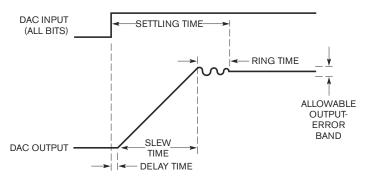

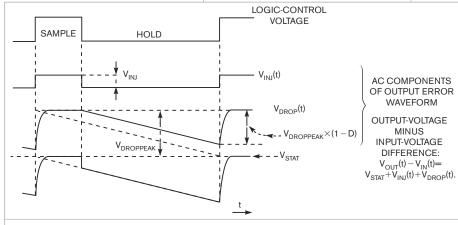

DAC settling time has three distinct components: delay time, slew time, and ring time (**Figure 1**). The delay time is small and is almost entirely due to propagation delay through the DAC and the output amplifier. During this interval, no output movement occurs. During slew time, the output amplifier moves at its highest possible speed toward the final value. Ring time defines the region in which the amplifier recovers from slewing and ceases movement within some defined error band. A trade-off between slew and ring time normally exists. Fastslewing amplifiers generally have extended ring times, complicating your amplifier choice and frequency compensation. Additionally, the architecture of fast amplifiers usually dictates trade-offs that degrade dc error terms (see **sidebar** "DAC-amplifier compensation").

#### DAC SETTLING TIME

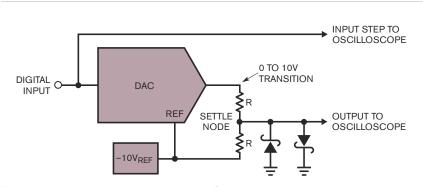

Engineers have previously measured DAC settling time with the false-sumnode technique (**Figure 2**). The resistors and DAC form a bridge-type network. With ideal components, the DAC output steps to the negative reference voltage when the DAC inputs move to all ones. During slew, the diodes, which limit the voltage excursion, bind the settling node. When settling occurs, the oscilloscope probe's voltage should be 0V. The resistor divider's attenuation means that the probe's output will be one-half of the DAC's settled voltage.

In theory, this circuit allows you to

observe settling to small amplitudes. In practice, you cannot rely on the circuit to produce useful measurements. The oscilloscope connection presents problems. As probe capacitance rises, ac loading of the resistor junction influences the settling waveforms. A 10-pF probe alleviates this problem, but its  $10 \times$  attenuation sacrifices gain. Probes with  $1 \times$  attenuation are not suitable

because of their excessive input capacitance. An active  $1 \times FET$  (field-effecttransistor) probe works but still presents a more significant issue: oscilloscope overdrive.

The clamp diodes at the settling node reduce swing during the amplifier's slewing, which prevents the circuit from overdriving the oscilloscope. Unfortunately, oscilloscope-overdrive-recovery

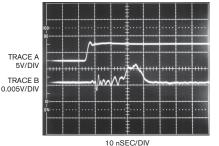

Figure 1 DAC settling time components include delay, slew, and ring time. Fast amplifiers reduce slew time, although longer ring time usually results. Delay time is normally a small term.

Figure 2 A popular summing scheme for DAC-settling-time measurement provides misleading results. An 18-bit measurement causes a more-than-800-times increase in oscilloscope overdrive.

#### AT A GLANCE

Deasuring anything to 1 ppm (part per million) is difficult, but measuring ac phenomena, such as settling time, is even more difficult.

Use a variable-transconductance amplifier instead of a diode bridge.

Trim out delays and parasitic effects when possible.

Be sure to verify your measurements.

characteristics vary widely, and manufacturers do not usually specify them. The 400-mV drop across the Schottky diodes means that the oscilloscope may see an unacceptable overload.

An oscilloscope typically undergoes a 2× overdrive when you set it to 50 mV/division while measuring to a 10bit resolution. A 10-bit resolution—10 mV at the DAC output—results in 5 mV at the oscilloscope. The desired 5mV baseline is just discernible. At 12bit or higher resolution, the measurement becomes hopeless. If you increase the oscilloscope's gain, you also increase overdrive-induced errors. At 18 bits of resolution, there is no chance of measurement integrity.

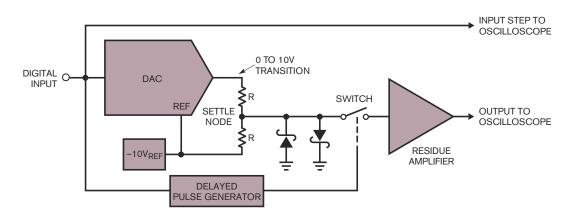

Measuring 18-bit settling time requires a high-gain oscilloscope that is also immune to overdrive. You can address the gain issue by using an external wideband preamplifier that accurately amplifies the diode-clamped settling node. Only classic sampling oscilloscopes, which vendors no longer manufacture, offer inherent overdrive immunity. However, you can construct a circuit that uses sampling techniques to avoid the overload problem. You can

Figure 3 This arrangement eliminates oscilloscope overdrive.

also endow the circuit with features for measuring 20-bit DAC settling time.

To measure 20-bit DAC settling time, you connect the settling point to the preamplified oscilloscope with a switch (Figure 3). You control the switch state with a delayed pulse generator, which you trigger with the same pulse that controls the DAC. You arrange the delayed pulse generator's timing so that the switch does not close until settling is nearly complete. In this way, you sample the incoming waveform in both time and amplitude. The oscilloscope never experiences overdrive, and no off-screen activity occurs.

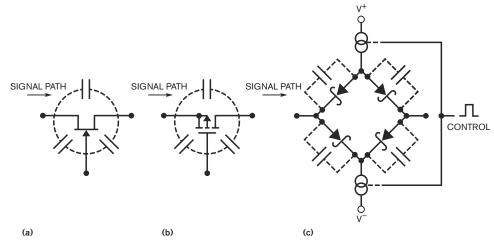

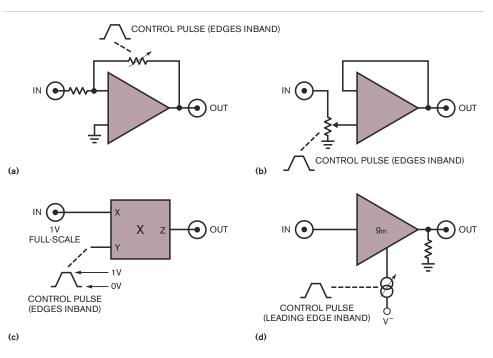

The sampling switch has stringent requirements. It must faithfully pass signal-path information without introducing alien components, including those from the switchcommand channel. Conventional choices for the sampling switch are JFETs (junction FETs), MOSFETs (metal-oxide-semiconductor FETs), and diode bridges (**Figure 4**).

The parasitic gate-to-channel capacitances of FETs result in a large feedthrough into the signal path from the gate drive. This feedthrough is many times larger than the signal you are observing, and it obviates the switch's purpose. The small parasitic capacitance and the symmetrical differential structure of a diode bridge tend to can-

cel the drive signal and result in low feedthrough. You must perform dc and ac trims and use complex drive and support circuitry with a diode bridge. You can reliably measure DAC settling time to 16bit resolution. Beyond 16 bits, residual feedthrough becomes objectionable, and you must use another approach.

You can construct a low-feedthrough, high-resolution switch using wideband active components. With this approach, you can maintain the switch's control channel inband because its transition rate is within the circuit's bandpass fre-

Figure 4 Conventional choices for sampling switches include JFETs (a), MOSFETs (b), and diode bridges (c).

Figure 5 Some low-feedthrough electronic-switch equivalents (a and b) are difficult to implement. You must optimize one practical scheme for low feedthrough on rising and falling control-pulse edges (c). In another, inherent bandwidth reduction minimizes falling-edge feedthrough (d).

quency. The circuit's wide bandwidth means that you can always control the switch's transition. You greatly reduce feedthrough by having no out-of-band response.

Some candidates for low-feedthrough electronic switches are theoretically possible but cumbersome to implement (Figure 5a and b). You must optimize others for low feedthrough on the rising and falling control-pulse edges because of the multiplier's unrestricted wideband response (Figure 5c). You can minimize falling-edge feedthrough by using the collapse of an amplifier's transconductance when the control pulse goes low (Figure 5d). This approach allows you to minimize the feedthrough of the control pulse's rising edge without regard to falling-edge effects. This feature provides a significant advantage for an electronic switch.

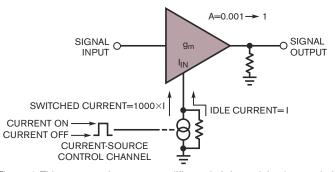

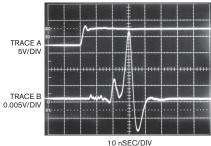

An electronic-circuit sampling switch uses a transconductance amplifier (Figure 6). The switch dynamics are exceptionally pure because the wideband control and signal paths faithfully track a 1000-to-1 transconductance change. You can carefully optimize the switched current source for the lowest feedthrough on the rising control edge without regard to the falling-edge characteristics. The transconductance collapses on the falling edge, which ensures low feedthrough for that condition. This technique prevents oscilloscope overdrive.

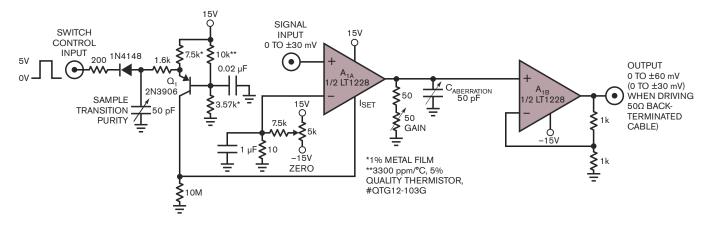

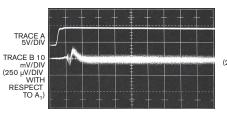

The detailed design switches signals over a  $\pm$ 30-mV range with peak control-channel feedthrough of only millivolts and settling times of less than 40 nsec (**Figure 7**). The unity-gain circuit approximates switch action by varying A<sub>1A</sub>'s transconductance. The amplifier and its transconductance control channel are wideband components, permitting them to faithfully track rapid variations in a transconductance setting. This characteristic means that the amplifier is always in control, affording clean response and rapid settling to the input's value.

Amplifier  $A_{1A}$  is the wideband transconductance amplifier. You set its voltage gain by the current magnitude into its  $I_{\text{SET}}$  (current-set) terminal and its output-resistor load. Amplifier  $A_{1B}$  unloads  $A_{1A}$ 's output. This amplifier provides a gain of two. When driving a back-terminated 50 $\Omega$  cable, however, its effective gain is unity at the cable's receiving end. The back termination establishes a 50 $\Omega$ signal-path environment. The switchcontrol input controls current source  $Q_1$ , which sets  $A_{1A}$ 's transconductance and gain.

$Q_1$  is gated off when you set the switchcontrol input at zero. The 10-M $\Omega$  resistor supplies 1.5  $\mu$ A into  $A_{1A}$ 's  $I_{SET}$  pin, which results in a voltage gain of nearly

Figure 6 This transconductance amplifier switch has minimal control-channel feedthrough.

zero. This action blocks the input signal. When you set the switch-control input high,  $Q_1$  turns on, sourcing 1.5 mA into the  $I_{SET}$  pin, in turn forcing maximum transconductance and causing the amplifier to assume unity gain and pass the input signal. You use trims for zero and gain to ensure accurate input-signal replication at the circuit's output. You purify turn-on switching with a 50-pF variable capacitor and use a 10-k $\Omega$  thermistor with a 3300-ppm/°C temperature coefficient at  $Q_1$ . This approach compensates  $A_{1A}$ 's transconductance temperature dependence to minimize gain drift.

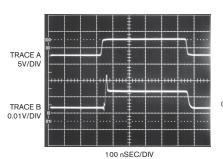

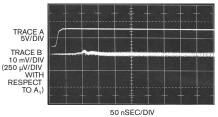

When you set the aberration capacitance to 35 pF, the circuit cleanly switches a 10-mV input signal (Figure 8). When the control input (Trace A) is low, no output (Trace B) occurs. When the control input goes high, the output reproduces the input with feedthrough settling in 20 nsec. You don't see turn-off feedthrough due to the transconductance reduction of 1000-to-1 and the attendant 25-fold decrease in the frequency bandwidth. You set the sweep speed to 10 nsec/division to examine the 0V-

settling details (**Figure 9**). The output (Trace B) settles to within 1 mV within 40 nsec after the switch control (Trace A) goes high. The aberration capacitance damps the peak feedthrough excursion of 5 mV. If you set this capacitance to 0 pF, feedthrough increases to 20 mV (**Figure 10**). Settling time to within 1 mV remains at 40 nsec. Setting this capacitance to 35 pF minimizes the feedthrough amplitude but yields seventimes-higher rise time than is possible with a setting of 0 pF (**Figure 11**).

The small dc and ac error of a transconductance switch accommodates the application's requirements. The low feedthrough becomes irrelevant because the DAC's ring-time interval buries the small time and amplitude error, pointing the way toward practical 1-ppm DACsettling-time measurements.

#### **MEASUREMENT METHOD**

You can combine this electronic switch with the DAC-amplifier summing method (Figure 12). You split the delayed pulse generator into independently variable delay and pulse-

Figure 7 A low-level, 100-MHz switch has minimal control-channel feedthrough.

Figure 8 The control input (Trace A) dictates a switch output's (Trace B) representation of a 0.01V-dc input. The control-channel feedthrough settles in 20 nsec. Turn-off feedthrough is undetectable due to deceased signal-channel transconductance and bandwidth. The aberration capacitance is 35 pF for this test.

generator blocks. You run the input step to the oscilloscope through a section that compensates for settling-timepath propagation delays. This path includes the settling node, the amplifier, and sample-gate delays. You drive the transconductance sampling switch from a nonsaturating residue amplifier, feeding the oscilloscope. Placing the sampling switch after the residue amplifier further minimizes sample-command feedthrough.

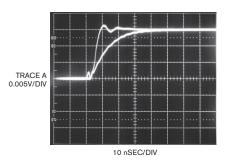

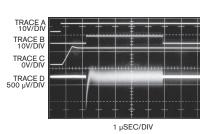

The 20-bit DAC-settling-time-measurement circuitry uses the input pulse to simultaneously switch all the DAC bits (Figure 13). You must use a modified circuit and a Microchip (www.microchip.com) PIC microcontroller for serial DACs (see sidebar "Settling-time measurement of serial DACs"). You also route this pulse to the oscilloscope through the delay-compensation network, which comprises CMOS inverters and an adjustable RC network. It compensates the oscilloscope's input step signal for the 44-nsec delay through the circuit-measurement path (see sidebar "Delay and circuit-trimming procedures"). You compare the DAC-amplifier output with the 10V reference using precision 10-k $\Omega$  summing resistors. The reference IC also furnishes the DAC reference, which makes the measurement ratiometric. A1, which also has voltage gain, unloads the clamped settling node. Amplifier A, has a clamped output and provides a total amplification of 40 referred to the summing node. A,'s output feeds the sampling-

Figure 9 For a 0V signal input, the output (Trace B) peaks at 0.005V before settling to 0.001V 40 nsec after the switchcontrol command (Trace A). Aberration capacitance is 35 pF for this test.

switch circuit. The potentiometer adjusts the circuit's gain.

You arrange the clamping and gain of  $A_1$  and  $A_2$  so that saturation never occurs. The amplifier is always in its active region. The input pulse triggers the 74HC123 dual one-shot. You control the pulse delay of the one-shot with a 20-k $\Omega$  potentiometer. If you set the delay appropriately, the oscilloscope sees no input signal until settling is nearly complete, thereby eliminating overdrive. You adjust the sampling switch's on-time so that you can observe all remaining settling activity.

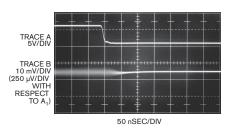

When the sample gate goes high, switching is clean, and you can easily observe the last millivolt of ringing time (Figure 14). The amplifier settles nicely to a final value. When the sample gate goes low, the transconductance switch goes off, and you can discern no feedthrough. There is never any offscreen activity, and the oscilloscope is never in overdrive.

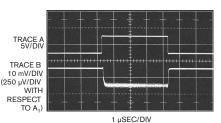

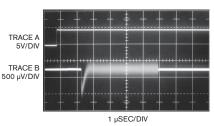

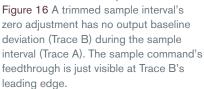

To achieve this level of performance, you must trim the circuit (see sidebar "Delay and circuit-trimming procedures"). If you do a poor sample-interval-zero adjustment, the circuit shifts the output baseline (Figure 15). A proper adjustment yields a continual baseline (Figure 16). You can see the barely visible sample-command feedthrough at Trace B's leading edge. Signal peaking goes to 350 µV, and settling is 50 nsec before your trimming aberrations and transition purity (Figure 17). By trimming these functions, you increase delay to 70 nsec from 20 nsec, but the signal peaks at only 50  $\mu$ V

Figure 10 The aberration capacitance is 0 pF; otherwise, conditions are identical to those in Figure 9. The feedthrough-related peaking increases to 0.02V, and the 0.001V settling time remains at 40 nsec.

Figure 11 The signal-channel rise times for 0 pF (left trace) and 35 pF (right trace) are 3.5 and 25 nsec, respectively. The switch-control input is high for this measurement.

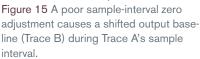

(Figure 18). Signal settling remains at 50 nsec. At the sample-command turnoff, the 1000-to-1 transconductance drop ensures a clean transition independent of the turn-on optimizing trims (Figure 19).

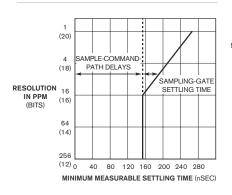

You can graph the minimum measurable settling time for a given resolution (Figure 20). Sample-command-path delays and sample-gate switching-residue profiles impose speed limitations on the circuit. You can measure settling time below 160 nsec at 16-bit resolution. For smaller signals, the sample gate's switching-residue profile dictates an increased minimum measurable settling time of 265 nsec at 20 bits. The DAC/amplifier, summing resistors, and residue amplifier/sampling switch impose circuit-noise limitations. Resolution beyond 15 ppm requires you to use filtering or noise-averaging techniques. You can drive the 74HC123's B2 input with a phase-advanced version of the

Figure 12 You can combine the electronic switch with the DAC-amplifier summing method.

Figure 13 A detailed DAC-settling-time-measurement circuit closely follows that of Figure 12. Optimum performance requires attention to layout.

Figure 14 The settling-time-circuit waveforms include a time-corrected input pulse (Trace A), a sample command (Trace B), a DAC output (Trace C), and a settling-time output (Trace D).

50 nSEC/DIV

Figure 17 The output response (Trace B) to a sample command's turn-on (Trace A) before you trim out aberrations and transition purity has a signal delay of 20 nsec. The aberrations peak at 350  $\mu$ V and settle in 50 nsec. You ground amplifier A<sub>1</sub>'s positive input using a 5-k $\Omega$  resistor for this figure and figures 15 and 16.

Figure 20 The sample-command-path delays and sample-gate-setting profile impose the minimum measurable settling-time-versus-resolution limits. Achieving a resolution beyond 15 ppm requires filtering or noise averaging.

pulse-generator input to largely eliminate sample-command-path-delay-induced error. This approach considerably improves minimum measurable settling time. You must use careful construction techniques and proven diligent measurements (see sidebar "Settling-time-

Figure 18 Trimming improves the output response (Trace B) to a sample command's turn-on (Trace A). The delay increases to 70 nsec, but aberrations peak at only 50  $\mu$ V, and the circuit settles in 50 nsec.

Figure 21 The 0 to 10V DAC with an unfiltered bandpass settles (Trace B) to 16 bits, or 15 ppm, in less than 2  $\mu$ sec after Trace A's time-corrected input step. The sample gate's feedthrough is well-controlled, indicating that higher resolution is possible without overdriving the oscilloscope. Noise is the limitation for this measurement.

circuit performance verification").

#### **CIRCUIT APPLICATION**

It is good practice to "walk" the sampling window backward in time from the settled region to the last 100  $\mu$ V or so of amplifier movement so that you can observe the cessation of ringing. The sampling-based approach provides this capability and is a powerful measurement

Figure 19 The output response (Trace B) to the sample command's turn-off (Trace A) shows a 1000-to-1 transconductance drop, ensuring a clean transition, independent of the trim state.

Figure 22 Reducing the measurement bandwidth to 250 kHz attenuates noise. The settling to 18 bits, or 4 ppm, requires approximately 5  $\mu$ sec. Filtering permits increased resolution, although the indicated settling time increases.

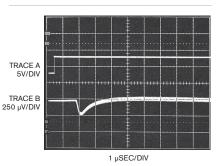

tool. Slower amplifiers may require extended delay, sampling-window times, or both, necessitating larger capacitor values in 74HC123 one-shot timing networks. Noise is the fundamental measurement limit with an unfiltered bandpass (**Figure 21**). The DAC (Trace B) settles to 16 bits, 1.7 μsec after Trace A's time-corrected input step. The DAC amplifier's compensation capacitor affects settling

Figure 23 You can discern 19-bit, or 2ppm, settling 9  $\mu$ sec after the input command with a 50-kHz bandwidth.

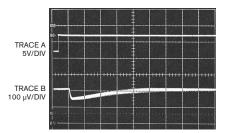

time (see sidebar "DAC-amplifier compensation"). Sample-gate feedthrough is undetectable, indicating that higher resolution is possible without overdriving the oscilloscope. Reducing the measurement bandwidth to 250 kHz attenuates noise (Figure 22). The 18-bit, or 4-ppm, settling requires approximately 5 µsec. The reduced bandwidth permits higher resolution, although the indicated settling time is likely pessimistic due to the filter's lag. Decreasing bandwidth to 50 kHz permits 19-bit, or 2-ppm, resolution with an indicated settling in 9 µsec (Figure 23). The same filter that permits high resolution also creates a longer settling time.

You can use noise-averaging techniques to measure settling time to 20 bits, or 1 ppm (10  $\mu$ V), without the time penalty of a bandlimiting filter (see Figure 24 in the Web version of this article at www.edn.com/100304df). You can adjust the DAC amplifier for overdamped, underdamped, and optimum responses. Using averaging eliminates noise, permitting you to determine settling time due to DAC dynamics. In this case, settling time ranges from 4 to 6 µsec, and fractional LSB (least-significant-bit) tailing is evident. This measurement determines DAC settling time due solely to dynamics that a step input initiates. For this reason, you can consider averaged results academic. Noise limits the measurement certainty at any given instant to 100  $\mu$ V. It is reasonable to maintain that this noise means that the DAC never settles inside this limit. The averaged measure-

+ For all sidebars related to this article, as well as a list of references, go to www.edn.com/100304df.

+ For more technical articles, go to www.edn.com/features.

ment defines settling time after you remove noise limitations.**EDN**

#### AUTHOR'S BIOGRAPHY

Ji a u c d

Jim Williams is a staff scientist at Linear Technology Corp, where he specializes in analog circuit and instrumentation design. He has served in similar capacities at National Semiconductor, Arthur D Little, and the Instrumentation Laboratory at the Massachusetts Institute of Technology (Cambridge, MA). A former student at Wayne State University (Detroit), Williams enjoys sports cars, art, collecting antique scientific instruments, sculpture, and restoring old Tektronix oscilloscopes.

Design your circuit, load virtually any type of substrate, send your file, and you'll have real working circuit boards in minutes. So real in fact, you'll achieve consistent, high resolution geometries that chemical etching can't even touch. From prototypes to medium-run production, the ProtoLaser S will liberate you from the board house.

```

www.lpkfusa.com/pls • 1-800-345-LPKF

```

long and intimate relationship exists between FPGAs (fieldprogrammable gate arrays) and the networking-equipment industry, dating back to the days of the dot-com bubble. In those heady times, networkhardware vendors were under intense pressure to get new

equipment out the door. With relatively slow transceivers and cabling holding back wire speeds outside the network cores, a features race developed among the vendors. The first one out the door with a new set of features claimed most of the pending orders, almost irrespective of price. If switch and router costs were to become ridiculous, the equipment vendors could just pass the cost along to networking start-ups, whose venture capitalists were always ready with another \$20 million check, or to service providers desperate not to fall behind.

This climate was perfect for FPGAs because they can support rapid change in design requirements and have moderate operating speeds, little sensitivity to power consumption, and almost no sensitivity to price. FPGA vendors began to sell their largest parts—chips with prices of more than \$1000 that had previously found use only a few at a time for prototyping or one-off projects—into the moderatevolume production networking boxes.

**BY RON WILSON • EXECUTIVE EDITOR**

FPGAS' EVOLVING ROLES IN NETWORKING HARDWARE MAY PREDICT THE FUTURE OF THE NEARLY UBIQUITOUS ICS.

ΔΓ

The impact on the FPGA industry was dramatic. The leading companies grew into billion-dollar businesses, creating the cash flow to fund much greater internal research and development. Altera and Xilinx moved from being conservative adopters of new process technology to being among the first few fabless companies at each new process node, which somewhat narrowed the performance gap between their chips and ASICs.

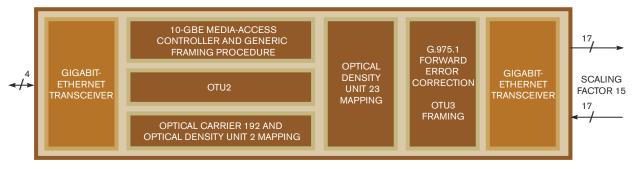

The way switch and router designers used the chips also changed. FPGAs had traditionally been convenient ways to implement glue logic. In the pressurized atmosphere of the Internet bubble, however, designers began to implement more complex functions, too-digitalsignal-processing algorithms, framers, and mappers, for example. This trend, in turn, drove the FPGA vendors to reflect the new applications' demands. They began seeding their logic fabric with powerful DSP engines, designing PHY (physical-layer) and MAC (media-access-control) hardware for high-speed serial I/Os onto the chips and enlarging on-chip memory structures to support greater data throughput. They also worked to make their design interfaces more powerful, recognizing that customers weren't just designing glue anymore.

But the dot-com bubble popped. Demand for network hardware plummeted and took FPGA orders with it. The FPGA-engineering work continued, however, even as the vendors scrambled to diversify their markets beyond networking. The result was that high-end FPGAs continued to include powerful features for switch and router applications, even though these features were often going into embedded-computing and control applications.

#### AT A GLANCE

**P**FPGAs (field-programmable gate arrays) and networking have had a long, symbiotic relationship.

The pressures that catapulted FPGAs into prominence in networking are reforming.

It is now feasible to implement most 40-Gbps line-card functions into one FPGA.

You will soon see networking applications profoundly change the nature of FPGAs.

#### **HERE WE GO AGAIN**

Now fast-forward to 2009 and a remarkably similar networking market. At every level—from the outskirts of the access network to the concentrators through which MAN (metropolitanarea-network) carriers route their traffic into the core—a scramble is under way to get more bandwidth and to support new payloads, such as video, and to move away from legacy networks to GbE (gigabit Ethernet).